International Journal of Advanced Research in Computer and Communication Engineering Vol. 2, Issue 9, September 2013

# **Radar Waveform Generator based on DDS**

B.Suresh<sup>1</sup>, M.V.Srikanth<sup>2</sup>

Student, ECE, Gudlavalleru Engg College, Gudlavalleru, India<sup>1</sup>

Associate professor, Gudlavalleru Engg College, Gudlavalleru, India<sup>2</sup>

Abstract- A radar waveform generator is implemented and it is designed by using directly digital modulation method based on DDS. It is able to generate arbitrary signals whose frequency amplitude and phases are controlled by the description words which will be given from external computer. Accurate waveforms are generated. By using Direct digital synthesis technique we can generate waveforms digitally . DDS technique is widely applicable and simple. Direct Digital Synthesizer (DDS) is a frequency synthesizer and it can generate arbitrary waveforms by using single, fixedfrequency reference clock. Some of the DDS Applications are: function generators, modulators. For implementing radar waveform generator along with DDS we need FPGA and PIC microcontroller. To generate the waveform using DDS we need to store the hexadecimal data into the internal registers of DDS chip along with that we need some control signals which will be generated using FPGA. First in PC we need to enter the information of the signal to be generated for that we need design a Graphical User Interface (GUI). In GUI we will enter the amplitude, frequency and phase of the waveform to be generated and then it has to covert that particular data into hexadecimal data based on the formulas mentioned in AD9910 datasheet, then it has to send that data to microcontroller through serial port. Now, microcontroller will receive that data from PC and then it has to send that data to the FPGA. FPGA will receive that data, along with that it has to generate some control signals and clock signals based on the control signals, received data has to be send to the internal registers of DDS chip.

Keywords: Direct Digital Synthesizer(DDS), Field Programmable Gate Array(FPGA), Graphical User Interface(GUI), microcontroller

## I. INTRODUCTION

produce and control accurate waveforms of different ,microcontroller and FPGA to control those AD9910 DDS frequencies. Some of the examples include agile frequency chips. Here we are designing four channel waveform sources with low spurious signal content and less phase generator using 4 AD9910 DDS chips, which are used to noise for communications, which will be used for produce industrial and biomedical applications. For those phase and frequency can be varied digitally. applications, we should be capable of generating an Here our main objective is to design a radar waveform adjustable waveform cost effectively and conveniently generator. For this first we have to design a GUI where we which is a key design consideration.

but among those direct digital synthesis (DDS) is most that information has to be converted into hexadecimal data flexible one. AD9910 DDS chip is used to generate an based on the formulas mentioned in AD9910 datasheet and analog signal ----usually a sine wave, but it can be used to then it will be sent to the PIC microcontroller from PC generate other signals also by generating a time varying using RS232 cable. By using that GUI we can also control signal in digital form and then by using D/A converter we the DDS chip. Microcontroller has to receive that can generate an analog signal. As DDS devices offer hexadecimal data from the PC using serial port and then it faster switching between output frequencies and fine has to send the data to FPGA through SPI. FPGA is used resolution in frequencies it is widely used.

,DDS devices consume less power and very compact .Here received hexadecimal data into the internal registers of in this design we are using AD9910 DDS chip it can DDS chips through SPI. Now that DDS will generate the generate arbitary signals with frequencies ranging from signal based on that hexadecimal data stored in the internal 1Hz to 400 MHz (based on a 1-GHz clock), with time registers. resolution of 64 bits. Devices with low cost and using new technologies are combined with DDS's which are used to generate waveforms and can be program them digitallymake DDS as attractive approach compared to other Direct digital synthesis (DDS) is a technique for

Generally for any equipment, it is important to readily be designed using multiple AD9910 DDS chips four identical waveforms whose amplitude,

have to enter the information required to generate an Several approaches are available for generating the signal analog signal such as phase, frequency and amplitude and to generate some clock and control signals to DDS chips As the technology advances in design and technology based on those control signals FPGA has to transfer that

#### **II DDS TECHNOLOGY**

solutions. Multichannel RADAR waveform generator can generating an arbitary waveforms such as sine wave by

International Journal of Advanced Research in Computer and Communication Engineering Vol. 2, Issue 9, September 2013

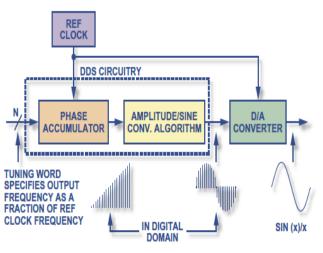

using time varying signal in digital form and then by using Amplitude/Sine Conv. Algorithm and then by using D/A digital to analog converter we will generate an analog converter analog sine wave is generated. signal.DDS has ability to generate and control an accurate signal that's why it is used by the most of the industries. Here phase -to - amplitude lookup table will be used to DDS technique is widely used for solving signal convert the phase-accumulator's instantaneous output value generation requirements for both communications and (32 bits for AD9910)-Among those 32 bits unneeded lessindustrial based applications because we can generate an significant bits will be eliminated by truncation-into the accurate analog signal using single chip with low cost and sine-wave amplitude information that will be applied to the power consumption.

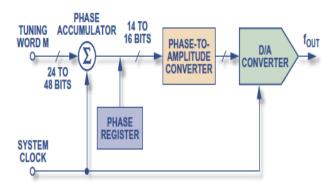

Fig1 shows the internal circuitry of a DDS device. its main components are phase-to-amplitude conversion (often a sine look-up table), phase accumulator and a DAC.

DDS can produces a sine wave at a given frequency. The frequency of the sinewave depends on two variables, the reference-clock frequency of the DDS and the binary number programmed into the internal registers (tuning word) of DDS.

Main input to the phase accumulator is frequency tuning word(FTW) i.e, binary number stored in the frequency register. If a sine look-up table is used, the phase accumulator will compute the phase(angle) address for look-up table, which will give the digital value of amplitude which corresponds to the sine of that phase angle to the DAC.Now, DAC will convert that digital value into corresponding value of analog voltage. To generate a sinewave of fixed frequency a constant value(it is determined by the binary number) is to be added to the phase accumulator for each clock cycle. If that constant value is large phase accumulator will step through the sine look-up table quickly and thus generate a high frequency sine wave.If that phase increment is small then phase accumulator will take more steps, accordingly it will generate a slower waveform.

Fig1.Components Direct Digital Synthesizer

Operation principle of DDS can be easily understood with the Fig.1. Frequency tuning word is given as input to the Phase accumulator and converts it into angular phase and then it is converted into the sine wave amplitudes by using

(14 -bit) Digital to Analog converter. The architecture of DDS exploits the symmetrical nature of a sine wave as it utilizes mapping logic to synthesize a complete sine wave from onequarter-cycle of data from the phase accumulator. The phaseto- amplitude lookup table will generate the remaining data by reading forward then backward through the lookup table. This is shown pictorially in Fig. 3.

Fig2.Signal flow through DDS

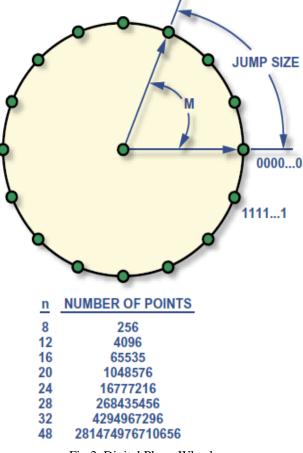

To understand the basic function consider sine wave oscillations as a vector rotating around a phase wheel as shown in Fig.3. The number of discrete points on the wheel can be determined by the resolution of phase accumulator. Each discrete point on the phase wheel represents its corresponding equivalent point on cycle of sine wave.

As vector rotates around the wheel, corresponding output sine wave will be generated. One complete cycle of sinewave will be generated when vector completes one revolution at a constant speed around the phase wheel. The phase accumulator is used to provide the equivalent of the vector's linear rotation around the phase wheel.

Each content of the phase accumulator represents its corresponding point on the cycle of output sine wave. The number of phase points on the wheel will be determined by the resolution (N) of phase accumulator. The output of phase accumulator is linear so, we cannot directly generate any wave expect ramp. So, we will use phase-to-amplitude lookup table to convert output value of phase accumulator to sine wave amplitude information and then it will be

International Journal of Advanced Research in Computer and Communication Engineering Vol. 2, Issue 9, September 2013

applied to D/A converter. The output frequency and length of the accumulator are related by the equation.

$$fo = \frac{M X fc}{2^N}$$

Where N denotes the number of bits used to represent the tuningword. Generally for AD9910 Frequency Tuning Word (FTW) is of 32 bit. Where:

- fo = output frequency of DDS

- M = frequency tuning word

- fc = internal clock frequency

- N =length of the phase accumulator in bits

Fig.3. Digital Phase Wheel

Here we are using AD9910 DDS chip it can generate waveforms whose frequencies are ranging from 1Hz to 400 MHz and clock frequency for AD9910 is 1 GHz and it has 14 bit Digital to Analog converter(DAC).

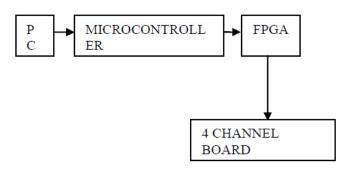

#### **III SYSTEM ARCHITECTURE**

## Fig.3. Block diagram

## A Graphical User Interface (GUI)

By using DDS we are generating analog signals. In order to generate the analog signals using DDS we need to store the corresponding information(hexadecimal data) of the analog signal into the internal registers of DDS. so we need design GUI which acts like an interface between PC and microcontroller and it has to convert the corresponding information i.e, amplitude, frequency and phase into corresponding hexadecimal data using the formulas mentioned in the AD9910 datasheet.along with that GUI has to send that hexadecimal data to the microcontroller through serial port from the pc.

| AD9910<br>PROFILES MULTICHIP SYNC            | OSK AND DIGITAL RAMP                    |                      |                                           |

|----------------------------------------------|-----------------------------------------|----------------------|-------------------------------------------|

| PROFILEZ VP SYNC SYNC ENABLE                 | ENABLE DIGITAL RAMP                     | ENABLE OSF           |                                           |

| PROFILE2 0/P SINC  FROFILE2                  | NODE<br>FREDUENCY AUTO CLR DIGI RAMP AC | ASF 0.99994 🚔        | REGISTER MAP                              |

| FRED 10 WINDOW - O ON FALLING                | O PHASE 📄 CLR DIGITAL RAMP AC           | USE EXT OSK OSK PN   | 0000 <u>0000008</u>                       |

| PHASE 1 10.0000 Mhz SYN ERR O ON RAISING     | O AMP 🔄 LOAD DRR                        | AUTO OSK             | CX01 0000000                              |

| ASF 1 0.99994 + deg CLEAR                    |                                         | AMP RAMP (0.0000     | 0x02 0000000                              |

|                                              | SWEEP FRED 10.00000 Mrz                 | AMP STEP             | 003 000000                                |

|                                              | R STEP SIZE 10.000000 Mitr              | 🗄 LOAD ARR           | 0x04 0000000                              |

| CONTROL<br>CLOCK FILLISE INTERNAL I/O UPDATE | 10.00000                                |                      | 0405 <u>000000000</u><br>0406 00000000    |

| EXCLA 100 IO UPDATE RATE PERIOD              |                                         | AUXILARY SOURCES     |                                           |

| 2 DWDER 8.00000 ÷                            |                                         | 0/P FREQ 10,000      | 0407 <u>0000000</u><br>0408 0000          |

| I ENA MUL IO UPDATE CLK DWDER                | F STEP SIZE 10.00000 Mbz                | PHASE OFF 1 0.000000 |                                           |

| M.FAC 7 🛊                                    | 1312 11                                 |                      | 0x09 <u>0000000</u>                       |

| ENABLE PFD TOTAL VO UPDATE PERIOD            | NO DWELL H UP DOWN                      |                      | DXDA 0000000                              |

| PFD X 10                                     | NO DWELLL PAUSE RAMP FIN                | LOAD                 | 0406 0000000000000000000000000000000000   |

| PFD ALIX DAC CONTROL                         | DERUG                                   |                      | 0/0C 0000000000000000000000000000000000   |

| CP CURF DAC GAIN CT                          | DUT DUT DUT                             | GrueBor24            | 0400 0000                                 |

| V00                                          | SIGNALSIPA) SIGNALSIPE) SIGNALSICTL)    | O PLL LOCK           | DADE 00000000000000000000000000000000000  |

| 420-485 MHZ A IOUT 8.73 S<br>482-562 MHZ     | 🖹 ISFC 📄 REGUD EN 📄 SCLK                | () SYNC SAMPLE ERROF | 0/0F 0000000000000000000000000000000000   |

| 562-656 MHZ E                                | EXT PD CRCTL AUTO APPLY                 | RAM SWEEP ERROR      | OK10 3FFF07h00CCCCCD                      |

| 832-920 MHZ POWER DOWN                       | RESET DUT OR HOLD                       | O DIGITAL RAMP OVER  | QX11 00000000000000000000000000000000000  |

| S20F108U MHZ * OIGITAL EXT PD MODE           | E I/O RESET                             | READ                 | 0/072 0000000000000000000000000000000000  |

| XTALO - EDAC FULL POWER DO                   | - III ANY                               |                      | QX13 0000000000000000                     |

| PLL LOC REFRES AUTO DAC FXT PD               | SERIAL VO                               |                      |                                           |

| C. DITY                                      | LOAD REG READ REG INDAT                 | E RAM LO WINDOW      | 0x14 00000000000000000000000000000000000  |

| SYSCLK 200 MHz 📋 ENA AUTO PD                 | REG AD + REG                            |                      | 0X15 00000000000000000000000000000000000  |

| ENABLE 10 SYNC                               |                                         |                      | DK16 000000000000000000000000000000000000 |

| ENABLE I/O SYNC                              | 6356 6546 6746 (93) (12)                | 2316 (55 (76         | REFRESH                                   |

| AUTO CLR PHASE ACCU                          |                                         |                      | LOAD                                      |

Fig.4. GUI

#### B Microcontrller

Here purpose of microcontroller is to receive the data sent from PC using GUI through serialport.we have to program the microcontroller such that it has to receive the data send

International Journal of Advanced Research in Computer and Communication Engineering Vol. 2, Issue 9, September 2013

by the pc through RS232 cable and then it has to send that hexadecimal data to the FPGA through serial peripheral Here using DSPIC33F interface(SPI). we are microcontroller.By using UART functions of DSPIC33F we can receive and store the data available at the serial port and by using SPI we can send that data to the FPGA.Here we are programming the DSPIC33F using MPLAB IDE and then by using PIC KIT3 programer, code will be dumped into the microcontroller.Fig.5. shows the compilation of the program written for the DSPIC33F in C language.

Fig.5. Compilation Of The C Program

## C Field Programmable Gate Array (FPGA)

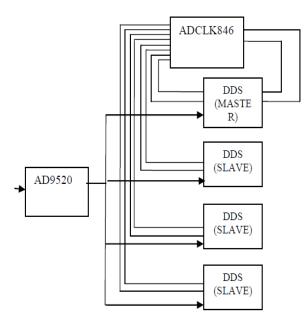

microcontroller through serial peripheral interface(SPI) clock frequency i.e, they will operate on the same internal and then it has to send that hexadecimal data into internal clock so they will produce identical signals. SYNC\_CLK registers of AD9910 DDS chips through SPI based on will be generated from the internal clock of the master some control signals, along with that it has to generate only by using frequency divider. AD9520 will be used to some clock signals to the AD9910 DDS chips.. PIC will distribute the clock signal generated by the FPGA to all the send the hexadecimal data received from the PC to the DDS chips. FPGA will provide the 10 MHz signal, but FPGA through SPI.

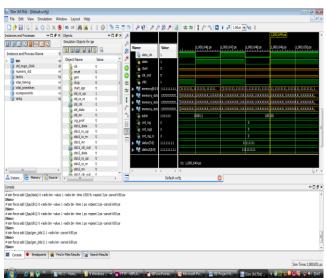

We have to program the FPGA such that it has to receive Ghz frequency. that hexadecimal data sent from microcontroller and then By using these devices the multichannel RADAR based on some control signals such as IO\_UPDATE it will waveform generator is implemented. Now in the GUI we send the data to DDS through SPI.FPGA is also used to have to specify the amplitude, phase and frequency of the clock generate signals using Digital Manager(DCM).It will generate 10 mhz clock using its DDS chip in which it has to operate generally DDS chip internal oscillator.Fig.6. shows the simulation of the code will operate in single tone mode in which DDS is used to written in VHDL.

Fig.6. Simulation Of FPGA Code D Four Channel Board

Here in this project our goal is to generate identical signals whose amplitude, phase and frequency should be varied according to our requirement. so for generating identical signals we need to synchronize DDS chips.

DDS chips has to generate the signals at a time i.e, they should start generating the analog signals at the same time so, that the analog signals will be synchronized. For synchronizing the DDS chips one of the DDS has to generate SYNC\_CLK and ADCLK846 will distribute that SYNC\_CLK to all the AD9910 DDS chips.

One which Generate the SYNC CLK acts like master and the remaining DDS chips will behave as slaves, thus the Here purpose of FPGA is to receive the data send from internal blocks of DDS chips are synchronized to single AD9910 need 1 Ghz clock frequency so, we will multiply the 10Mhz signal using PLL multiplier to get desired 1

> Clock desired signal and we need set the mode of the AD9910 generate the signal based on the information present in its internal registers . After setting all the controls of DDS chips in GUI, it will generate corresponding hexadecimal data and then it will be send to the microcontroller.Now microcontroller will receive that data through serialport and then it will send that data to FPGA through SPI and then FPGA will receive that data and send it to the the internal registers of DDS.

International Journal of Advanced Research in Computer and Communication Engineering Vol. 2, Issue 9, September 2013

Fig.7. 4 channel board

## **IV RESULTS**

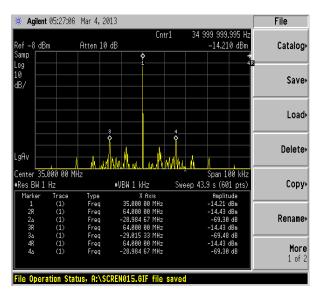

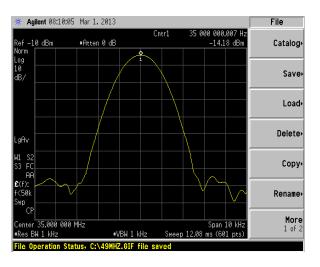

The below figure shows output of DDS applied to AGILENT spectrum analyzer. It shows single frequency output spectrum in which mark1 specifies the frequency of signal which is 35 Mhz with an amplitude of 14.210 dbm.

Fig.8. Single frequency output spectrum

Below figure shows AD9910 DDS output which is directed into spectrum analyzer and zoomed in.

Fig.9. DDS output direct into spectrum analyzer

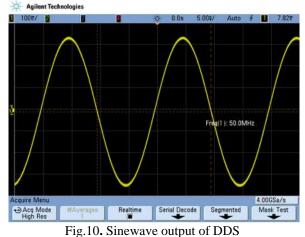

Below Fig.10. shows the sinewave output generated by AD9910 DDS whose output frequency is 50MHz.

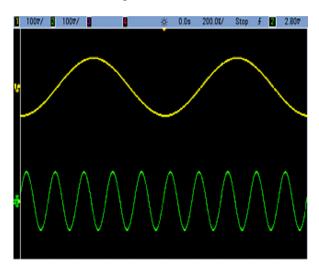

Below Fig.11. shows the sinewave outputs generated by two different DDS chips.

Fig.8. Sinwave outputs of two different DDS chips

International Journal of Advanced Research in Computer and Communication Engineering Vol. 2, Issue 9, September 2013

## V CONCLUSION

In this paper, the Four channel waveform generator is designed using Four AD9910 DDS chips. This design shows the architecture of multichannel radar waveform generator which is designed using AD9910 DDS chips, FPGA and PIC microcontroller.

#### REFERENCES

- Zhidong Shao; Aiyu Lu; Minggang Chai, "Design of radar controller based on FPGA", Publication Year: 2011, Page(s): 3423 - 3426.

- [2] Gangele, S.; Desai, N.M.; Senthil Kumar, R.; Vachhani, J.G.; Gujraty, V.R. "ISRO programmable digital waveform generator", Publication Year: 2009, Page(s): 25 – 30.

- [3] Wenfeng Dong; Quan Liu; Shirui Peng; Haihong Li "Design and realization of arbitrary radar waveform generator based on DDS technology", Radar Handbook Edition 3, Publication Year: 2010, Page(s): 1-534 - 1-537.

- [4] Paul P. Sotiriadis, Senior Member, IEEE, and Kostas Galanopoulos, Student Member, IEEE, "Direct All-Digital Frequency Synthesis Techniques, Spurs Suppression, and deterministic Jitter Correction", IEEE transactions on circuits and systems—I: regular papers, vol. 59, no. 5, may 2012.

- [5] Venceslav F. Kroupa, Senior Member, IEEE, Vaclav Cızek, Jarmil Stursa, and Hana Svandov, "Spurious Signals in Direct Digital Frequency Synthesizers Due to the Phase Truncation", IEEE transactions on ultrasonics, ferroelectrics, and frequency control, vol. 47, no. 5, september 2000.

- [6] J. Vankka, "Methods of Mapping from Phase to Sine Amplitude in Direct Digital Synthesis," in Proc. 1996 IEEE Frequency Control Symposium, Honolulu, Hawaii, July 5-7, 1996, pp. 942-950.

- [7] J. Vankka, "Methods of Mapping from Phase to Sine Amplitude in Direct Digital Synthesis," IEEE Transactions on Ultrasonics, Ferroelectrics and Frequency Control, vol. 44, pp. 526-534, March 1997.

- [8] J. Vankka, "Digital Modulator for Continuous Modulations with Slow Frequency Hopping," in Proc. IEEE Personal, Indoor and Mobile Radio Communications Conference, Oct. 15-18, 1996, Taipei, Taiwan, pp. 1039-1044.

- [9] J. Vankka, M. Kosunen, M. Waltari, K. Halonen, "Direct Digital Syntesizer with on-Chip D/A-converter," in Proc. 14th NORCHIP conference, 4-5 November 1996, Helsinki, Finland, pp. 20-27.

- [10] "FPGA-Based Design, Implementation, and Evaluation of Digital Sinusoidal Generators", 2008 IEEE.

- [11] Analog Devices, A technical tutorial on digital signal synthesis, 1999.

- [12] Microchip, MPLAB\_User\_Guide\_51519c

- [13] Digital frequency synthesis demystified / Bar- Giora Goldberg, 1999.

- [14] Digital modulation techniques / Fuqin Xiong,2000.

- [15] Xilinx Spartan-3E Evaluation Kit User Guide

- [16] Analog Devices, AD9910 Data Sheet.

- [17] Analog Devices, ADCLK846 Data Shee.t

- [18] Analog Devices, AD9520 Data Sheet.

## BIOGRAPHY

**B.Suresh** has completed B.Tech (ECE) in Avanthi institute of engg and tech and he is pursuing his M.Tech in Embeded System at Gudlavalleru Engineering College, AP.

**Mr. M.V.Srikanth** is working as Assistant Professor in Gudlavalleru Engineering College, AP. He completed his P.G. in communications as specialization at CBIT. Currently he is pursuing his PH.D in the area of image processing at JNTU-K.So far he has 5.6 years of teaching experience and published 1 IJ paper